热线

手机

由于信号供电电压逐步降低,产品尺寸缩小等因素的影响,信号-电源协同仿真,芯片-封装-PCB电源完整性的协同仿真在当下产品开发变得越来越普遍。对于信号-电源的协同仿真,我们一般称之为Power-Aware仿真分析,即考虑电源对信号的影响,这在DDR信号中更为明显。对于电源的芯片-封装-PCB协同仿真,芯片模型常见Spice网表,是从芯片网表抽取出的模型,如常见的CMP模型,而PKG/PCB则是PDN模型,当然包含去耦电容。下面我们就这2部分内容进行学习说明。

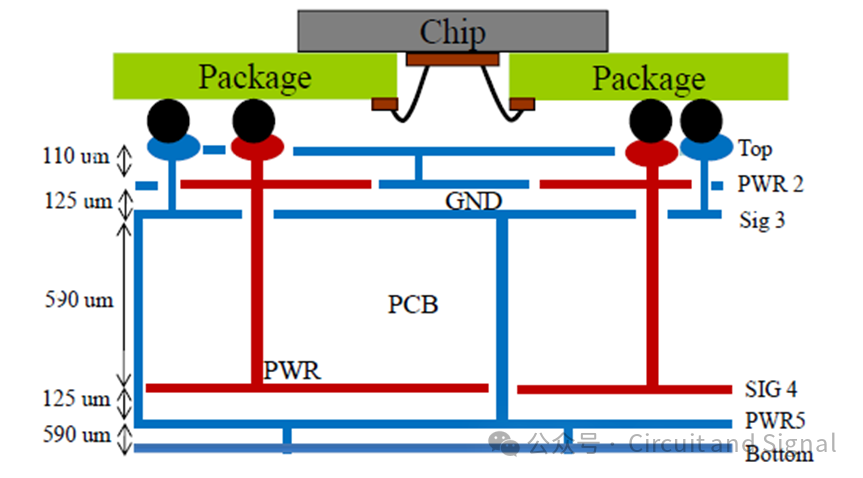

DDR3的物理结构如下图所示:

芯片朝下,导线与单层封装基板连接,封装与PCB通过BGA连接。PCB是6层FR4板,具有复杂的电源/地网络走线。下面介绍三个不同层次的PDN等效模型的提取方法,并验证所构建模型的准确性。

§

PCB的PDN模型

§

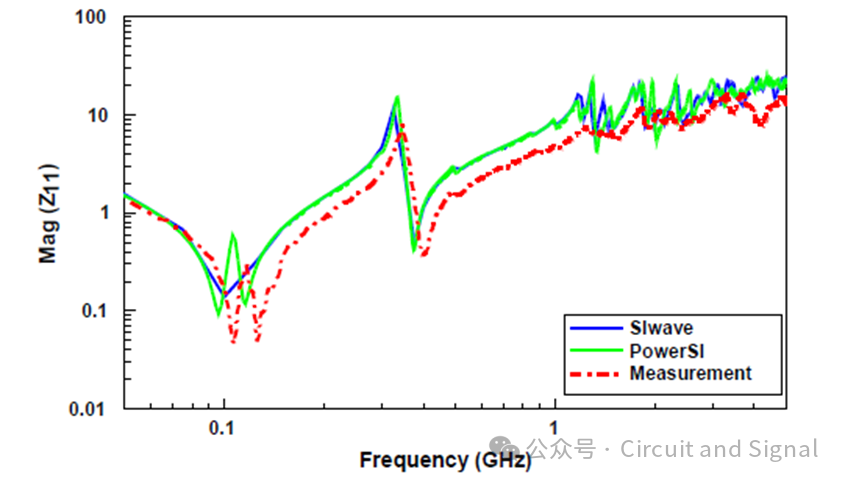

PCB物理结构过于复杂,因此我们采用EDA工具如PowerSI或者SIWAVE来抽取PCB的PDN参数,结果如下图所示。这是裸板的PDN结果,可以看出:PDN在低频时表现为一个小电容器(1.63 nF),在约100MHz以上变为电感。在325MHz附近可以看到谐振效应.

§

PKG的PDN模型

§

封装模型既可以用Q3D来提取RLGC参数,也可以用EDA工具提取PDN模型,整个操作过程和PCB类似。

§

芯片模型

§

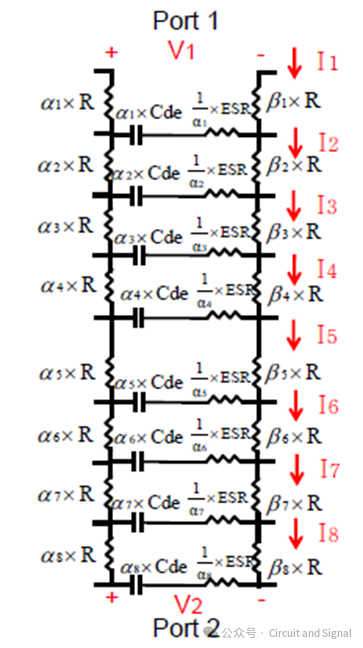

芯片模型可以用如RedHawk软件来抽取CPM模型,也可以基于测试创建等效模型,在我们无法借助EDA工具获取CPM模型时,基于测试构建等效模型就成为了重要手段,这也是我们关注的重点。等效模型的构建基于3个假设:

1.电源/地网络的寄生电阻(R)与电源/地网络之间的距离成正比

2.片上去耦电容(Cde)的值与电源/地之间的距离成正比

3.片上去耦电容的电阻(ESR)与电源/地之间的距离成反比

令尔法对应第(n-1)个pad与第n个pad的距离与电网处1个pad与第9个pad的距离之比,β对应(n-1)个pad与n个pad的距离与接地网处1个pad与第9个pad的距离之比。基于上述三个假设,可以构建芯片的等效模型,如下图所示。

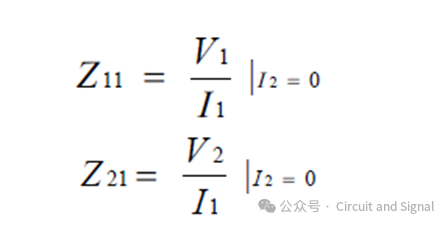

为了推导R、Cdie和ESR的值,它们必须以Z参数的形式与测量结果联系起来。

Z参数的定义由式给出

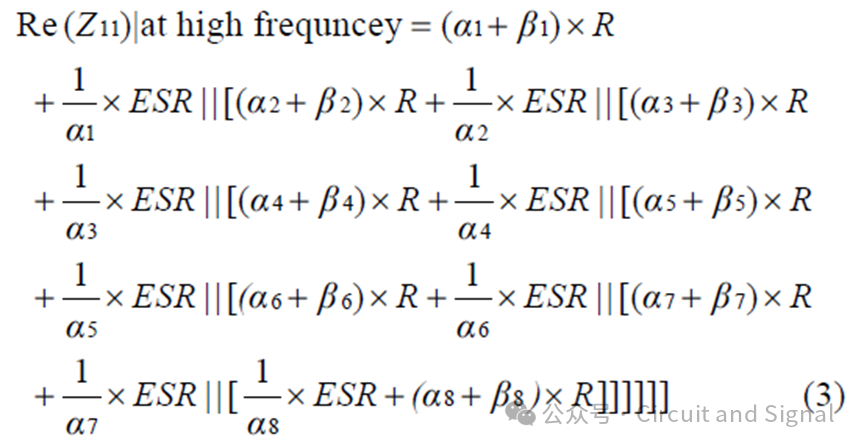

上图芯片模型的Z11的高频实部为:

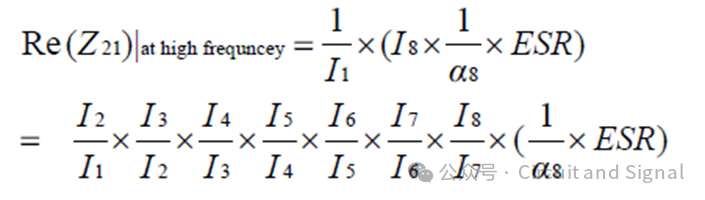

Z21的高频实部为:

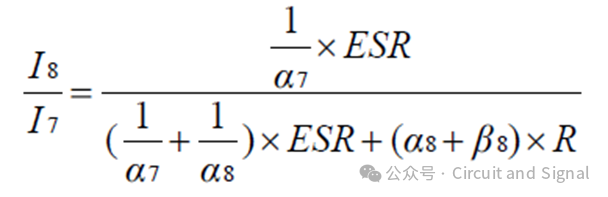

In与I(n-1)的电流比很容易得到,定义I8与I7的电流比为:

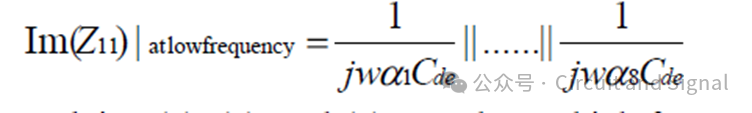

芯片模型的低频Z11可以表达为:

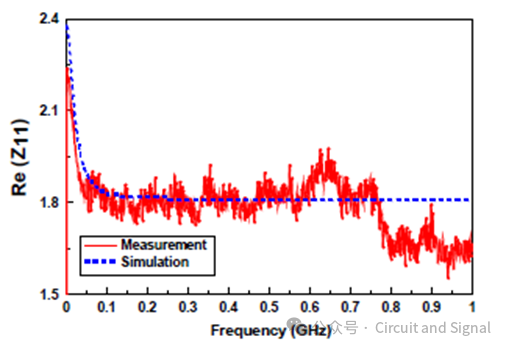

联立上面式子就可以得到R, Cdie, ESR参数,基于该参数构建的模型的仿真结果和测量结果对比如下:

·

PI-SI联合仿真

·

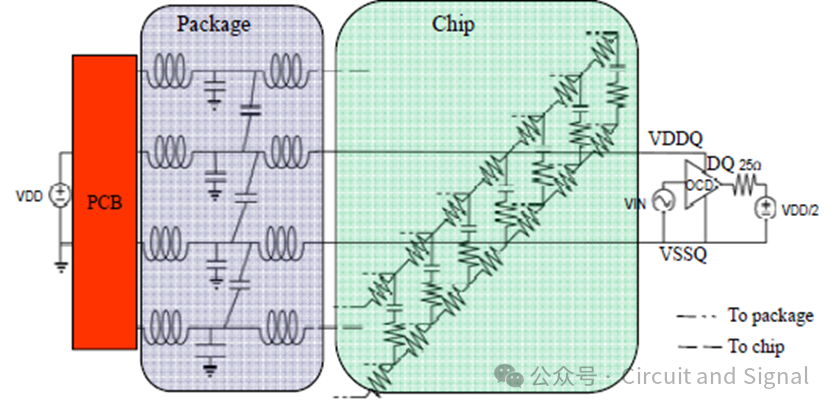

整个系统仿真结构图如下所示:

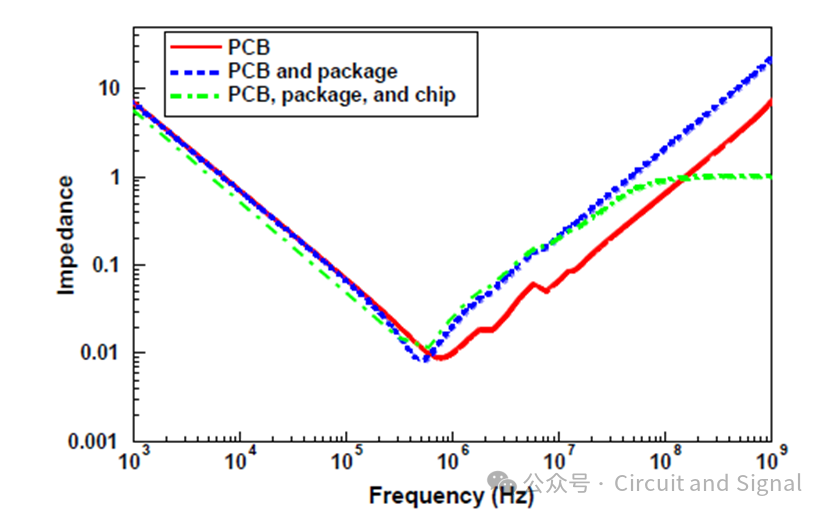

就PDN部分,仿真结果如下图所示:

在1MHz到10MHz之间,整个系统的PDN和PKG+PCB的阻抗相似,在100MHz以上系统的PDN变为常数,这是片上去耦电容和电阻作用的结果。由于去耦电容和芯片PDN并联的ESR的缘故,因此,PDN阻抗与较高频率下的C值和ESR有关。然而,在较低频率下,完整PDS的输入阻抗小于芯片PDN和去耦电容的寄生电阻值。因此,并联的影响在低频时对整个PDN阻抗没有影响。

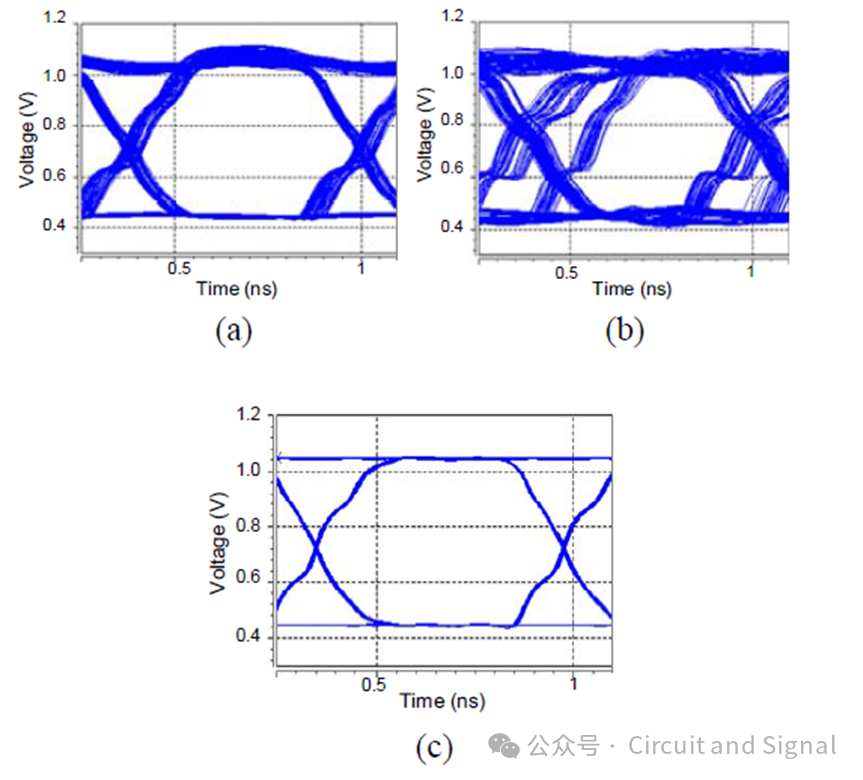

下面是信号-电源联合仿真结果,我们测试了3个case:信号的频率是800M,各自对应的PDN阻抗分别是5.6欧,17.8欧和1.06欧,仿真结果如下图所示:

可以看到眼图结果和PDN结果是匹配的,因此在DDR信号的分析中,电源-信号的联合仿真是非常有必要的,可以尽最大程度降低信号异常的风险。

免责声明:本文采摘自Circuit and signal,本文仅代表作者个人观点,不代表金航标及行业观点,只为转载与分享,支持保护知识产权,转载请注明原出处及作者,如有侵权请联系我们删除。